# AnalogDialogue

# StudentZone– Activity: MOS Transistor Common Source Amplifier

**Doug Mercer**, Consulting Fellow and **Antoniu Miclaus**, System Applications Engineer

# Objective

The purpose of this activity is to investigate the common source configuration of a MOS transistor.

# Background

The common source amplifier is one of three basic single-stage amplifier topologies. The MOS version functions as an inverting voltage amplifier. The gate terminal of the transistor serves as the input, the drain is the output, and the source is common to both input and output (it may be tied to the ground reference or the power supply rail), which gives rise to its common name.

#### **Materials**

- ADALM2000 Active Learning Module

- Solderless breadboard

- Five resistors

- One 50 kΩ variable resistor, potentiometer

- One small signal NMOS transistor (ZVN2110A)

#### **Directions**

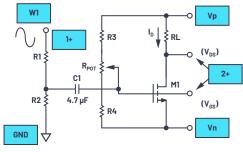

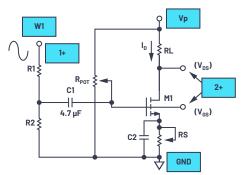

The configuration, shown in Figure 1, demonstrates the NMOS transistor used as the common source amplifier. Output load resistor  $R_L$  is chosen such that, for the desired nominal drain current  $I_D$ , the voltage appearing at  $V_{DS}$  is approximately halfway between the positive supply voltage  $V_P$  (+5 V) and the negative supply

voltage  $V_{N}$  (-5 V). Adjustable resistor  $R_{POT}$  sets the nominal bias operating point for the transistor ( $V_{GS}$ ) to set the required  $I_{D}$ . Voltage divider R1/R2 is chosen to provide a sufficiently large attenuation of the input stimulus from waveform generator W1 such that the amplitude of W1 is approximately the same as the signal amplitude seen at  $V_{DS}$ . This is done to more easily view the waveform generator W1 signal, given the rather small signal that will appear at the gate of the transistor,  $V_{GS}$ . The attenuated W1 signal is ac coupled into the gate of the transistor with 4.7 µF C1 so as not to disturb the dc bias condition.

Figure 1. Common source amplifier test configuration.

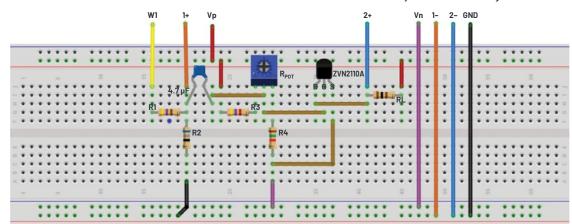

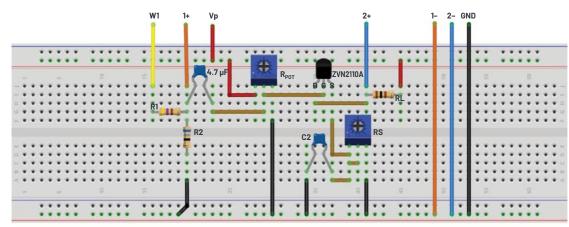

#### **Hardware Setup**

The waveform generator W1 should be configured for a 1 kHz sine wave with 3 V amplitude peak-to-peak and 0 V offset. The setup should be configured with Scope Channel 1+ connected to display the output W1. Scope Channel 2 (2+) is used to measure alternately the waveform at the gate and drain of M1.

Figure 2. NMOS diode breadboard circuit.

#### Procedure

Turn on the power supplies connected to the drain (V  $_{\rm P}$  = +5 V) and source (V  $_{\rm N}$  = -5 V) of the MOS transistor.

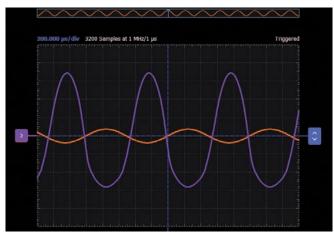

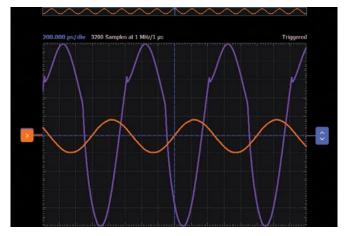

Configure the oscilloscope instrument to capture several periods of the input signal (orange trace) and the output signal (purple trace).

#### A plot example is presented in Figure 3.

Figure 3. Scopy plot of a common source amplifier test circuit.

The voltage gain, A, of the common source amplifier can be expressed as the ratio of load resistor R<sub>L</sub> to the small signal source resistance r<sub>s</sub>. The transconductance, g<sub>m</sub>, of the transistor is a function of the drain current I<sub>0</sub> and the so-called gate overdrive voltage, V<sub>ss</sub>-V<sub>th</sub>, where V<sub>th</sub> is the threshold voltage.

$$g_m = \frac{2I_D}{V_{GS} - V_{th}} \tag{1}$$

The small signal source resistance is  $1/g_m$  and can be viewed as being in series with the source. Now with a signal applied to the gate, the same current flows in  $r_s$  and the drain load  $R_L$ . Thus, the gain A is given by  $R_L \times g_m$ .

$$4 = -g_m R_L \tag{2}$$

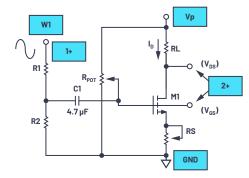

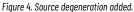

#### **Adding Source Degeneration**

Common source amplifiers give the amplifier an inverted output and can have a very high gain and can vary widely from one transistor to the next. The gain is a strong function of both temperature and bias current, and so the actual gain is somewhat unpredictable. Stability is another problem associated with such high gain circuits due to any unintentional positive feedback that may be present. Other problems associated with the circuit are the low input dynamic range imposed by the small signal limit; there is high distortion if this limit is exceeded and the transistor ceases to behave like its small signal model. When negative feedback is introduced, many of these problems are reduced, resulting in improved performance. There are several ways to introduce feedback in this simple amplifier stage, the easiest and most reliable of which is accomplished by introducing a small value resistor in the source circuit ( $R_s$ ). This is also referred to as series feedback. The amount of feedback is dependent on the relative signal level dropped across this resistor.

The source degeneration gain equation:

$$A = -\frac{g_m R_L}{1 + g_m R_S} \tag{3}$$

#### **Additional Materials**

One 5 k0 variable resistor, potentiometer

#### Directions

Disconnect the source of M1 from ground and insert R<sub>s</sub>, a 5 k $\Omega$  potentiometer, as shown in Figure 4. Adjust R<sub>s</sub> while noting the output signal seen at the drain of the transistor. The gain of the circuit can be adjusted by modifying the value of the R<sub>s</sub> potentiometer.

#### **Hardware Setup**

The waveform generator W1 should be configured for a 1 kHz sine wave with 3 V amplitude peak-to-peak and 0 V offset. The setup should be configured with Scope Channel 1+ connected to display the output W1. Scope Channel 2 (2+) is used to alternately measure the waveform at the gate and drain of M1.

Figure 5. Source degeneration added to a breadboard connection.

#### Procedure

Turn on the power supplies connected to the drain ( $V_P = 5$  V).

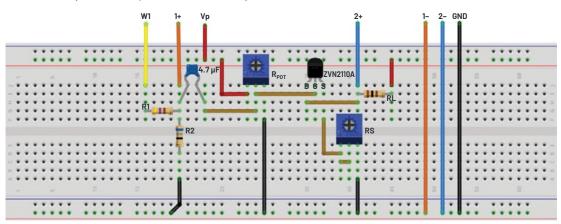

Configure the oscilloscope instrument to capture several periods of the input signal (orange trace) and the output signal (purple trace).

Figure 6. Source degeneration added to a Scopy plot.

# Increasing the AC Gain of a Source Degenerated Amplifier

Adding the source degeneration resistor has improved the stability of the dc operating point at the cost decreased amplifier gain. A higher gain for ac signals can be restored to some extent by adding capacitor C2 across the degeneration resistor  $R_{s_{\rm F}}$  as shown in Figure 7.

Figure 7. C2 added to increase ac gain.

#### **Hardware Setup**

The waveform generator W1 should be configured for a 1 kHz sine wave with 3 V amplitude peak-to-peak and 0 V offset. The setup should be configured with Scope Channel 1+ connected to display the output W1. Scope Channel 2 (2+) is used to measure alternately the waveform at the gate and drain of M1.

#### Procedure

Turn on the power supplies connected to the drain ( $V_P = 5$  V).

Configure the oscilloscope instrument to capture several periods of the input signal (orange trace) and the output signal (purple trace).

A plot example is presented in Figure 9.

Figure 9. C2 added to a Scopy plot.

### Questions

- How does adding negative feedback help to stabilize the dc operating point?

- ► For the source degeneration circuit setup, what is the effect on the voltage gain, A, by increasing R<sub>s</sub>?

You can find the answers at the StudentZone blog.

Figure 8. Breadboard connection with C2 added.

# About the Author

Doug Mercer received his B.S.E.E. degree from Rensselaer Polytechnic Institute (RPI) in 1977. Since joining Analog Devices in 1977, he has contributed directly or indirectly to more than 30 data converter products and he holds 13 patents. He was appointed to the position of ADI Fellow in 1995. In 2009, he transitioned from full-time work and has continued consulting at ADI as a Fellow Emeritus contributing to the Active Learning Program. In 2016 he was named Engineer in Residence within the ECSE department at RPI. He can be reached at *doug.mercer@analog.com*.

# About the Author

Antoniu Miclaus is a system applications engineer at Analog Devices, where he works on ADI academic programs, as well as embedded software for Circuits from the Lab<sup>®</sup>, QA automation, and process management. He started working at Analog Devices in February 2017 in Cluj-Napoca, Romania. He is currently an M.Sc. student in the software engineering master's program at Babes-Bolyai University and he has a B.Eng. in electronics and telecommunications from Technical University of Cluj-Napoca. He can be reached at *antoniu.miclaus@analog.com*.

For regional headquarters, sales, and distributors or to contact customer service and technical support, visit analog.com/contact.